PDP-11 Timing Repair

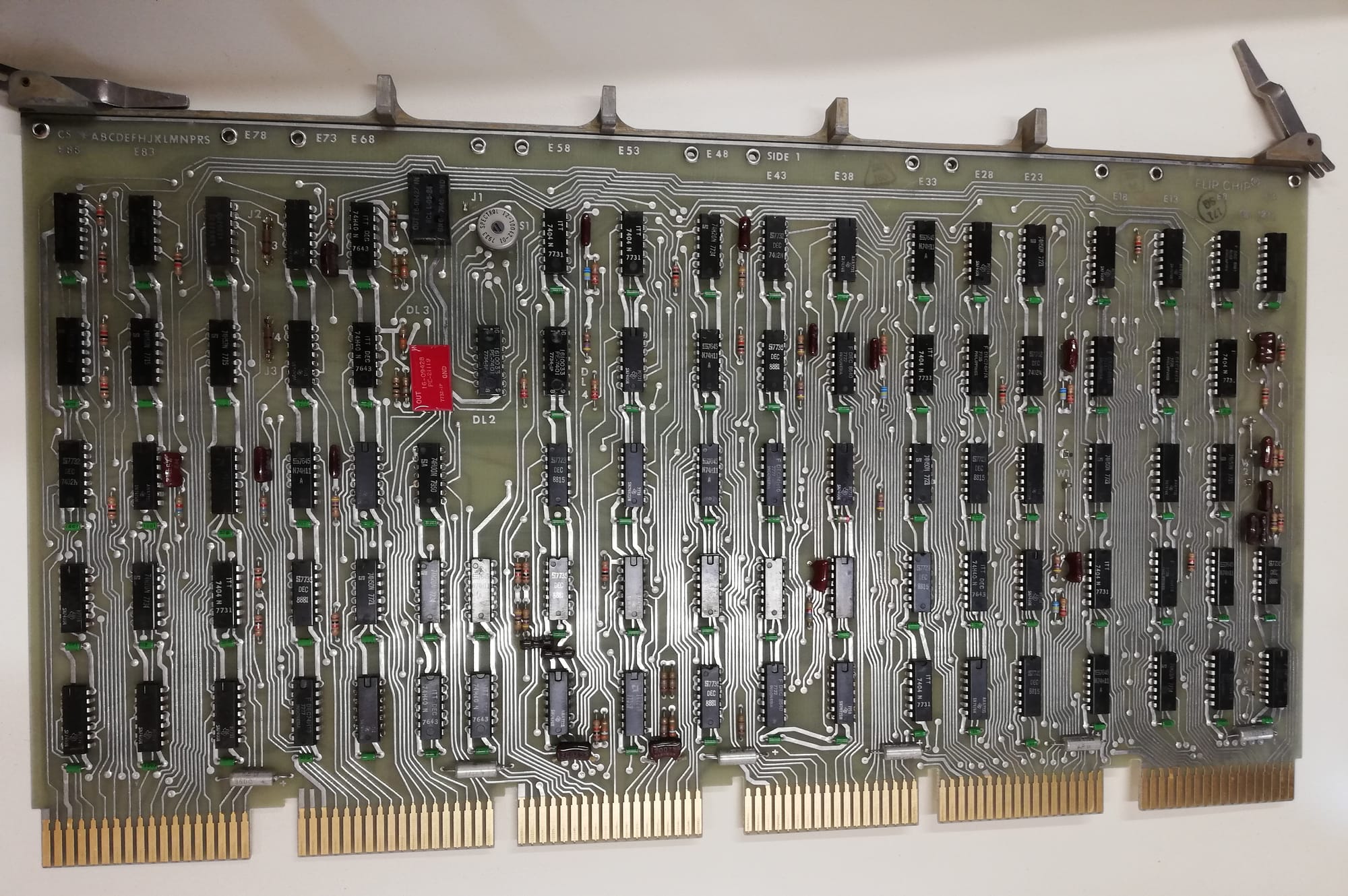

The next part of my PDP-11 to fix is the M7234 - Timing card. It's responsible for the system clock and unibus bus operations. In this situation, the issue presented itself as a fault related bus operations.

Symptoms

Console

Any operations involving the unibus did not work. Examine, deposit, and load address all caused the system to malfunction.

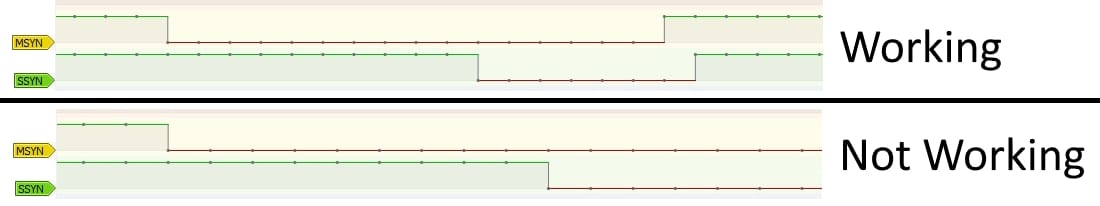

Unibus

Viewing the Unibus with the logic analyser showed that the MSYN and SSYN lines would be asserted, but MSYN was not deasserted as was expected.

The above image is of a DATI transaction. You can see that the MSYN does not get deasserted as it should.

Working Theory

From my initial diagnostics, I believed the issue was with the MSYN and SSYN logic in some way. I was particularly interested in why MSYN was not being deasserted. Two plausible failures came to mind:

- SSYN was being read from the bus incorrectly and not making its way through the bus logic.

- The mechanism that deasserts MSYN was not functioning.

Debugging MSYN

The most obvious place to start was to understand how MSYN is set and cleared. After spending some time looking at the schematics and manuals, I learned that MSYN is a flip-flop (K4-4 E10). MSYN is set at the start of DATI transaction and is cleared when the system's clock is restarted.

More specifically, when the system clock resumes a special flag known as IDLE is set/unset. This IDLE signal is specifically used to clear the MSYN flip-flop.

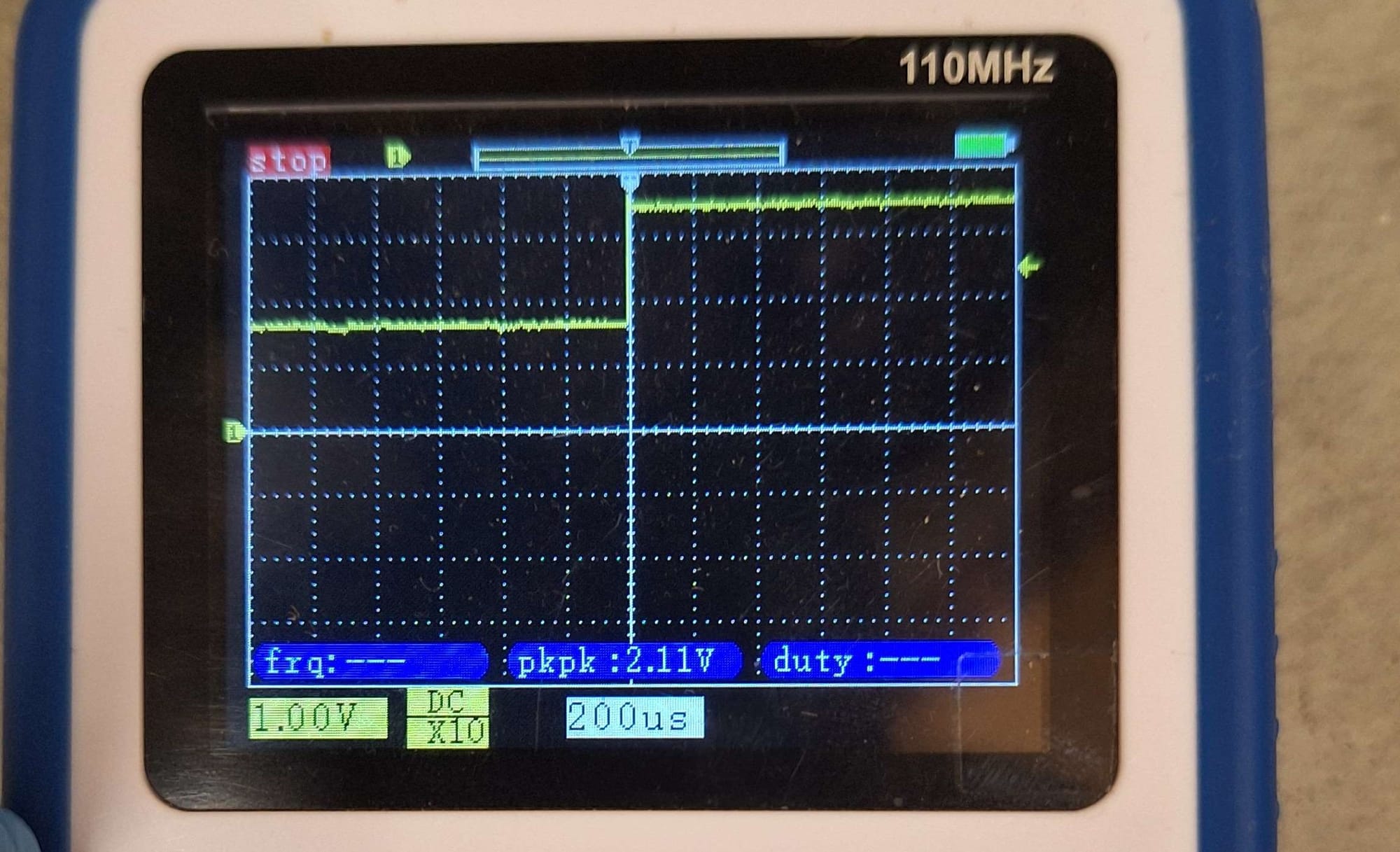

With a general understanding of how the MSYN flip-flop gets set and cleared, I spent some time watching it on the scope. I could clearly see that it was being set active correctly, and the flip-flop outputs looked good. Moving to the clear input, I was able to see that there was the expected pulse, but the flip-flop was not being cleared.

Looking closely at the clear signal (IDLE), you can see that the logic high is 3.5v and the logic low is 1.7v! Neither of those values is particularly good, but the logic low, the state we're specifically interested in, is well outside the expected range for a TTL chip (below 0.8v). This could possibly explain why the MSYN flip-flop is not getting cleared!

The Fix

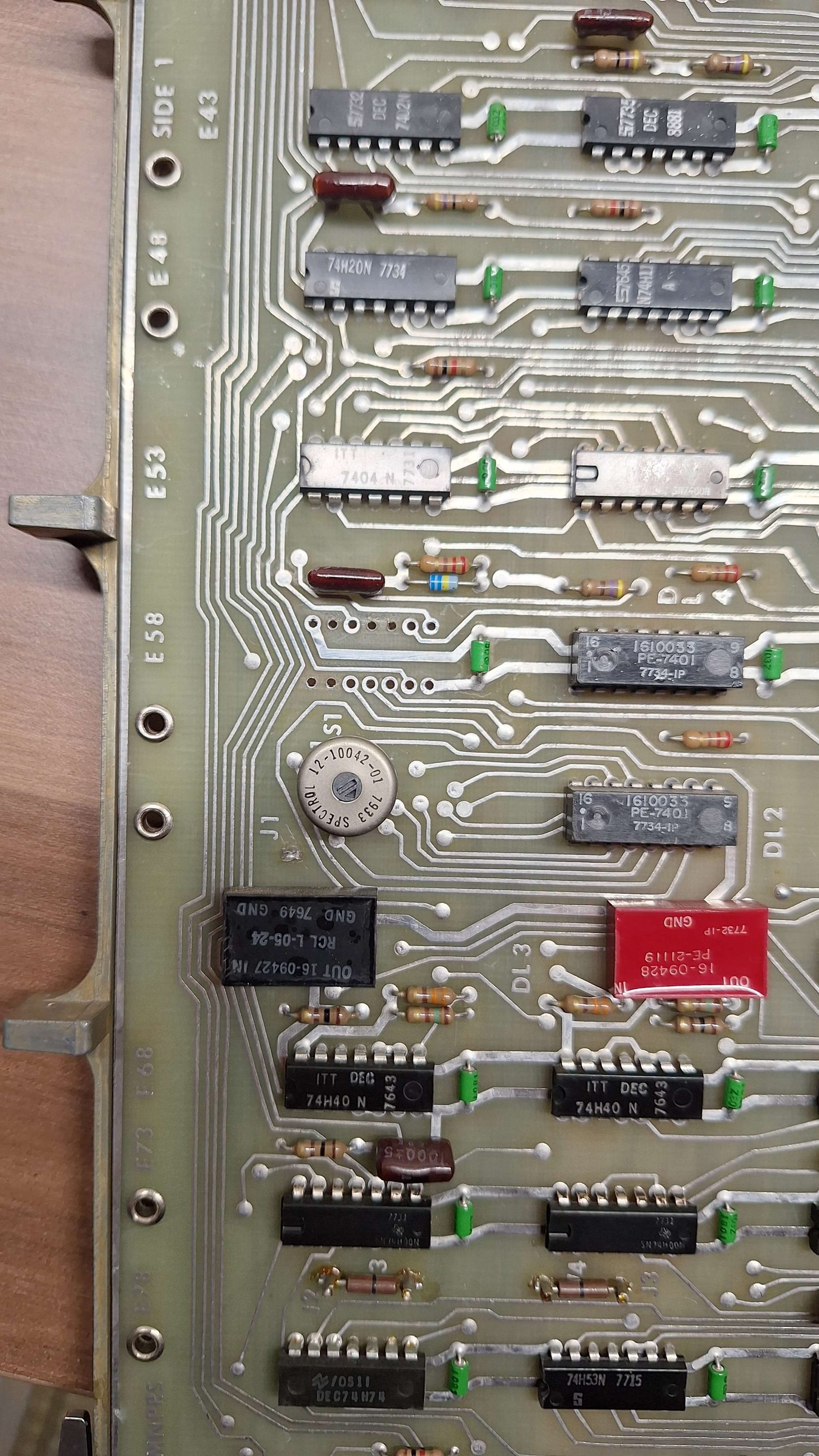

Having identified the likely problem, the question became, what chip was that fault?

The clear signal (IDEL L) comes from a NOT gate (K4-2 E58) directly fed by the IDEL flip-flop. Quickly examining the NOT gates input showed no issues. So the failure is either the NOT gate output, the flip-flop input, or both. There's no real way to know without cutting traces. So I decided to remove the NOT gate (7404) chip and test it out of the circuit.

Testing the 7404 with a tester and on a breadboard, I was able to verify that the chip was bad. Two of the six NOT gates had failed. There were no guarantees that the flip-flop was not also broken, but with a bit of luck, it would be fine.

I replaced the 7404 with one from the spare parts collection and reinstalled the timing card. To my satisfaction, when I powered up the system, it functioned as expected. Double-checking the flip-flop clear line, it looked healthy with a nice strong signal.

Conclusion

It goes to show that just a single bad chip can completely fundamentally cripple the the computer. It makes me wonder how many non-critical failures there are in the computer that I am just now aware of yet.

Hopefully, the replacement chip will keep running, and it won't need to be replaced anytime soon.