PDP-11 Timing Repair - SACK Time Out

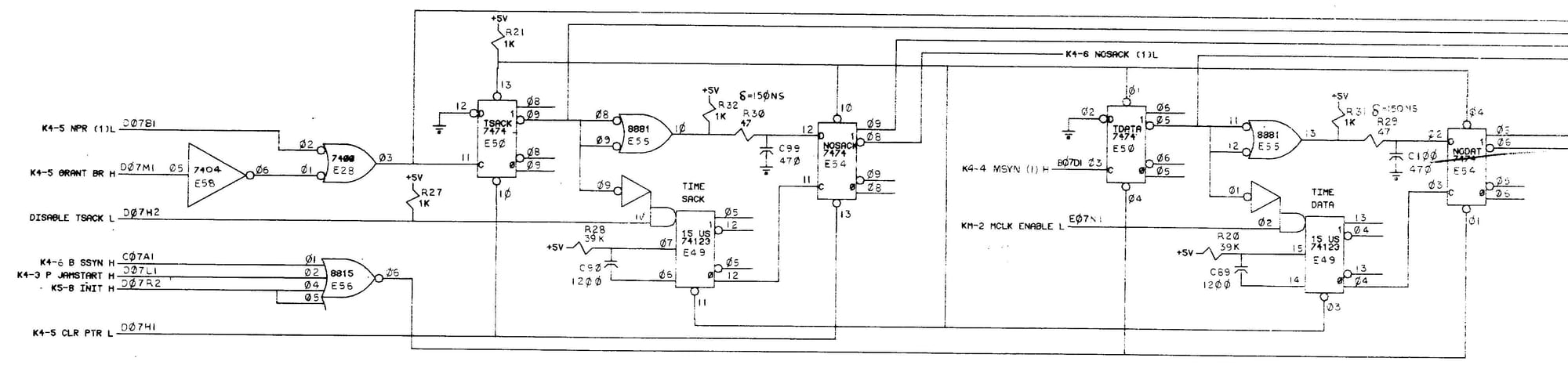

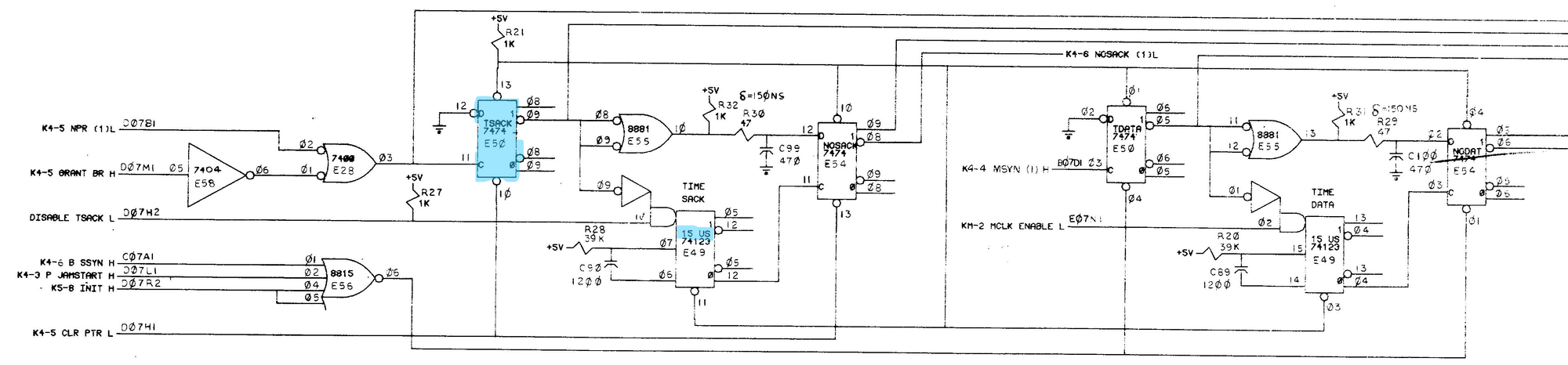

This time I have the Timing card (M7234) on the workbench. The Timing card has the system clock and bus interface logic. It is comprised of a collection of one shot time is flip-flops and delay lines. This makes diagnosing problems difficult.

Symptoms

- When pressing "START" on occasion the program will stall!

- The floating point instruction tests are stalling!

Investigation

I did the usual trick of swap the boards around until I was able to pinpoint the fault down to the timing card. Having spent some time working on the timing card before I knew there was a significant chance the fault was just a broken flip-flop. I spent about half a day checking the outputs of flip-flops to make sure that they were not obviously broken. I found no obvious faults.

Having a closer look at when the CPU it was stalling, I could see that the system stopped one cycle after an asynchronous bus restart. Digging into that further, I spent about a day and a half with the logic analyser looking at various parts in the clocking and reclock logic. I found no obvious faults.

Bus transaction Investigation

Having exhausted all the easy options it was time to move onto understanding why the FIS tests where getting stuck and when. When I was running the tests it was unclear whether the FIS tests where stopping at the same point or at different points. So I decided initially that I would record the bus transaction for the working and not working Timing card.

Looking at the bus transaction it was fairly obvious where processor was getting stuck but why. We can see that on the working board BG4 is asserted then de-asserted while on the other board it was asserted and the CPU stopped.

What followed was a day of reading the "PDP-11 Bus Handbook 1979". Long story short DL11 (UART) was requesting the bus to start an interrupt but it would cancel it. The CPU would eventually try to grant the bus the to DL11 but by that point it no longer needed it. The bus grant would go unanswered and the CPU ground to a halt. Ordinarily the the BG wound timeout, in this case the timeout counter never started.

Fixing the Problem

Once I knew that that BG was meant to timeout after about 15us it was simple to track down the relevant circuitry. Starting at the NOSACK flip-flop I saw no output or input activity. Moving back down the chain I looked at TSTACK, I found that it was not latching any data. Replacing the flip-flop solve the stalling issue when running the FIS tests. Unfortunately, the CPU can still stall on "Start".